Overcoming the analog computing challenge, the team created a robust binarized neural network powered by a miniature solar cell optimized for edge applications. The design, featuring digital near-memory computing, eliminates the need for calibration, excelling under diverse conditions. The circuit matches lab bench performance in high illumination, seamlessly transitioning to approximate low-light computing. Simulations show misclassifications under low illumination occur primarily in challenging cases, paving the way for self-powered AI in health, safety, and environment monitoring.

Previous research has extensively utilized AI in embedded applications like patient monitoring and industrial safety. Processing data at the edge is preferred to enhance security and minimize energy consumption. However, deploying AI in extreme-edge environments faces challenges due to high power consumption, often necessitating reliance on the "cloud" or "fog."

Memristor-based systems offer a promising solution, reducing AI energy consumption and enabling the creation of self-powered edge AI systems. Researchers employ memristors as non-volatile memories, ensuring the retention of information even when energy depletes.

Demonstrator Fabrication and Analysis

The fabrication process of the demonstrator involved utilizing a low-power 130-nanometer foundry process for the metal-oxide-semiconductor (MOS) part up to the fourth layer of metal. Researchers fabricated memristors by composing them of a titanium nitride/hafnium oxide/titanium/titanium nitride (TiN/HfOx/Ti/TiN) stack, which was then meticulously fabricated on exposed vias. The memristor structure exhibited a 300-nanometer diameter, and a subsequent step involved depositing a fifth layer of metal on top of the structure.

The design of the memristor-based Binarized Neural Network incorporated a hybrid complementary metal-oxide-semiconductor (CMOS)/nanotechnology integrated circuit with distributed memory modules. Memory module design included array and peripheral circuits, employing a full-custom flow under the cadence virtuoso electronic design automation (EDA) tool. In fabricating the solar cell, a semiconductor stack was grown on a gallium arsenide (GaAs) substrate using molecular beam epitaxy.

Researchers initiated fabrication by defining the front metal grid through standard photolithography techniques. Subsequently, the solar cell underwent characterization under a halogen lamp to facilitate variable-illumination experiments. They measured the system with a lab-bench power supply on the packaged version, with the integrated circuit connected to an STMicroelectronics 32-bit flash series number performance line graphic package type package variant (STM32F746ZGT6) microcontroller unit and other equipment. Using commercial integrated circuit design tools, researchers obtained energy consumption estimates through computer simulations.

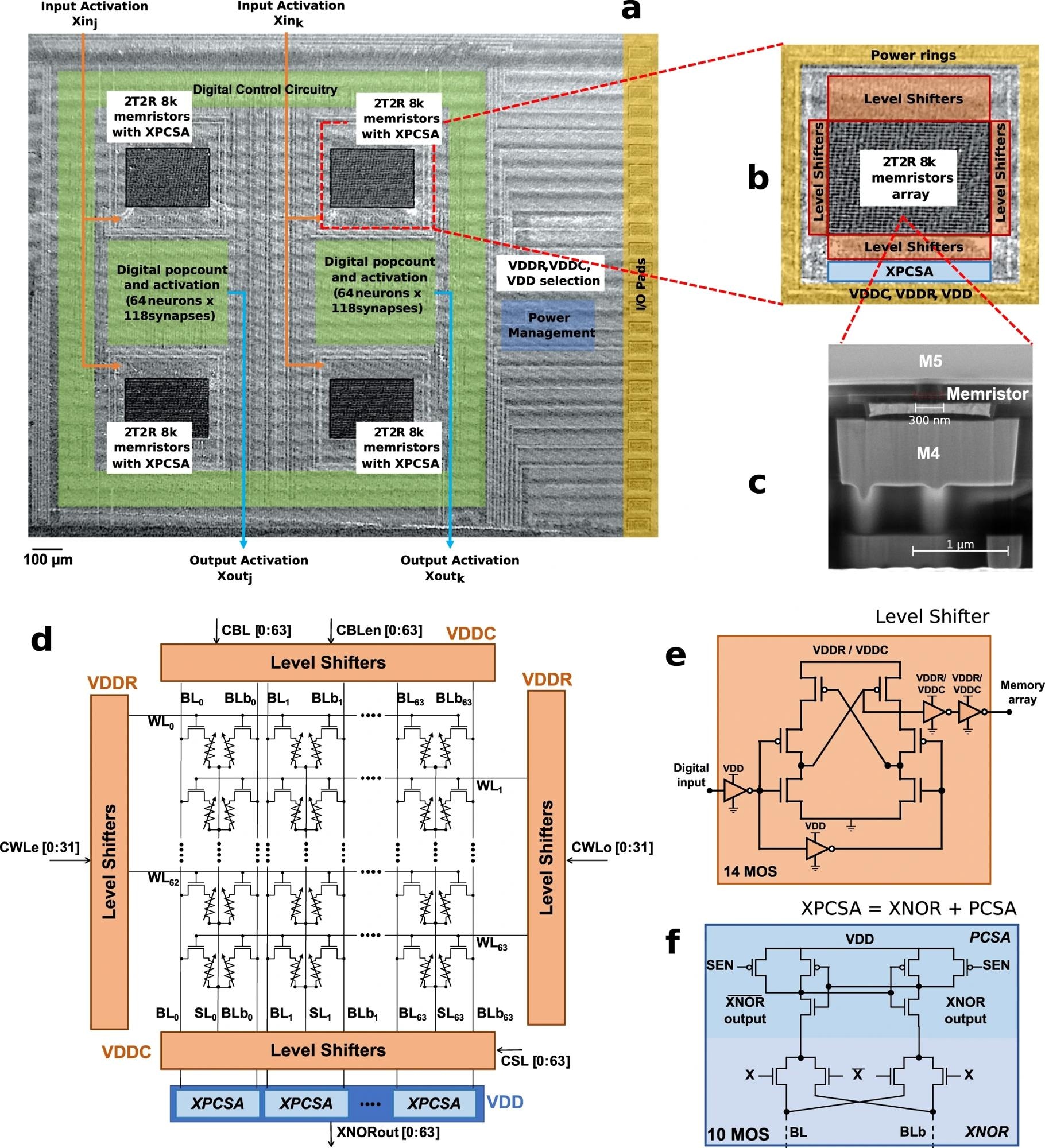

a Optical microscopy image of the fabricated die, showing four memory modules and their associated digital circuitry and power management unit. b Detail on one of the memory modules. c Cross-sectional scanning electron micrograph of a hybrid CMOS/memristor circuit, showing a memristor between metal levels four and five. d Schematic of a memory module. For each operation mode, biasing conditions for WL, BL, and SL are given with respect to the power domain (VDDC, VDDR) and VDD. e Schematic of the level shifter, used in d for shifting digital voltage input to medium voltages needed during programming operations or nominal voltage during reading operations of the memristors. f Schematic of the differential pre-charge sense amplifier PCSA, used to read the binary memristor states, with embedded XNOR function, to compose a XPCSA: it computes an XNOR operation between input activation X and weight (memristor value) during bit-cell sensing.

a Optical microscopy image of the fabricated die, showing four memory modules and their associated digital circuitry and power management unit. b Detail on one of the memory modules. c Cross-sectional scanning electron micrograph of a hybrid CMOS/memristor circuit, showing a memristor between metal levels four and five. d Schematic of a memory module. For each operation mode, biasing conditions for WL, BL, and SL are given with respect to the power domain (VDDC, VDDR) and VDD. e Schematic of the level shifter, used in d for shifting digital voltage input to medium voltages needed during programming operations or nominal voltage during reading operations of the memristors. f Schematic of the differential pre-charge sense amplifier PCSA, used to read the binary memristor states, with embedded XNOR function, to compose a XPCSA: it computes an XNOR operation between input activation X and weight (memristor value) during bit-cell sensing.

The memristor arrays' consumption was determined through circuit simulations, while the rest of the system was analyzed using the cadence voltus power integrity solution framework. Researchers conducted neural network simulations for the Modified National Institute of Standards and Technology (MNIST) and Canadian Institute for Advanced Research - 10 (CIFAR-10) tasks using fully connected and convolutional architectures. In their training process, researchers employed the PyTorch deep learning framework for all neural network simulations, initially training the networks without errors and subsequently actively introducing errors during the inference step.

Resilient Binarized Neural Network

In this study, the authors introduce a novel binarized neural network machine based on distributed memristor modules. Binarized neural networks, characterized by synaptic weights and neuronal activations assuming binary values (+1 and −1), offer a resource-efficient solution for image and signal processing tasks, particularly suitable for extreme-edge applications. The hardware system was fabricated with hafnium-oxide memristors integrated into the back end of a CMOS line, replacing vias between metal layers four and five. The system comprises four memristor arrays, each containing 8,192 memristors, and operates with a low-power 130-nanometer process node.

Researchers have incorporated two memristors per synaptic weight, programmed in a complementary fashion, to ensure reliable operation under unpredictable power supply conditions. A dedicated logic-in-memory precharge sense amplifier performs multiplication by reading the state of the memristors and executing an exclusive NOR (XNOR) operation. This differential approach enhances circuit robustness by minimizing the impact of memristor variability and symmetrically handling power supply voltage fluctuations.

The system operates by computing the values of all output neurons in parallel, utilizing near-memory computing principles to save energy. The non-volatile storage of synaptic weights by the memristors allows researchers to turn the system off and on at any time, effectively reducing power consumption during idle periods. Researchers program weights before the inference process, conducting a forming operation on each memristor before initiating the first programming operation.

The authors conducted comprehensive characterizations of the system's functionality, accuracy, and energy consumption across various supply voltages and operating frequencies. The measurements demonstrate the circuit's resilience to fluctuating power supplies, and the energy consumption analysis reveals its efficiency under different conditions.

Furthermore, the study explores the system's performance under harvested energy from a miniature solar cell. By directly connecting the circuit's power supply pads to the solar cell without additional interface circuitry, the authors showcase the adaptability of their binarized neural network to energy harvesting applications.

Regarding neural network simulations, the authors map neural networks to the hardware using a technique that subdivides layers into binarized arrays. It demonstrates the system's accuracy on tasks such as MNIST handwritten digit recognition and CIFAR-10 image recognition. The study highlights the circuit's self-adaptive approximate computing feature, indicating its ability to maintain functionality under varying levels of energy availability.

Conclusion

To sum up, the study introduces a resilient and efficient memristor-based binarized neural network machine, demonstrating its potential for extreme-edge applications and energy harvesting scenarios. The research provides valuable insights into the system's design principles, operational characteristics, and adaptability to challenging environmental conditions.